TAB BOOKS/No. 1099

## How to Build Your Own Working 16-Bit Microcomputer

\$ 7 QE

Everything you need to know to use the new superadvanced TI 9900 CPU single-chip processor.

By Ken Tracton

CONTRACTORIES

## How to Build Your Own Working 16-Bit Microcomputer

#### Other TAB books by the author:

- No. 771 Integrated Circuits Guidebook

- No. 861 Display Electronics

- No. 960 IC Function Locator

- No. 1000 57 Practical Programs & Games in BASIC

- No. 1055 The BASIC Cookbook

- No. 1085 24 Tested, Ready-to-Run Game Programs in BASIC

- No. 1095 Programs in BASIC for Electronic Engineers, Technicians & Experimenters

## How to Build Your Own Working 16-Bit Microcomputer

## By Ken Tracton

#### **FIRST EDITION**

#### FIRST PRINTING-APRIL 1979

#### Copyright © 1979 by TAB BOOKS

Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Cover photo courtesy of Electronic Technician/Dealer magazine.

# Preface

Microprocessors, those tiny slices of processing power, are rapidly growing more potent. The first microprocessor was suitable only for simple controller operations (such as the control unit of a microwave oven). Its immediate successors had a greatly increased instruction set, but were limited to 4-bit data chunks. These chips remain with us, as the processors in calculators. Within a year, both 8- and 12-bit units reached the market, and the microcomputer as we know it was born. Now, we are able to build 16-bit processors that can compete on equal terms with mini computers, both in speed and in capability.

One such device, the 9900 CPU by Texas Instruments, is widely considered to be the most advanced single-chip processor yet built. This text describes how to design a working *micro-computer* with the 9900 and its support family.

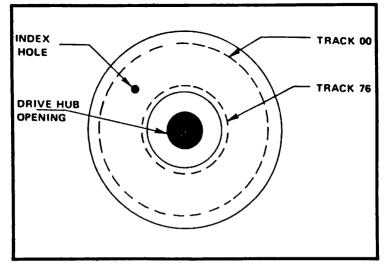

It begins with a minimum unit, useful for machine language and control functions, and progresses to an information processing system that can include time-sharing, a variety of languages, floppydiscs, disc-drives, cassette tape units, and a host of different terminals. En route, it discusses each type of interface required, how to use it, and how, on occasion, to circumvent its necessity.

The appendices include 9900 instruction codes, pinouts of the 9900 support chips as described in the text, and a listing of the ASCII code in near-universal use. I would like to thank Mr. Alec Grynspan, who compiled the vast amount of data required for this text and assisted me in many different capacities. I must also give special thanks to Mr. Dave Campbell, representative of Texas Instruments for his cheerful and understanding help which made this book possible, and of course Texas Instruments who created the 9900 family of micro-processor devices and peripherals, who graciously supplied the materials that allowed me to evaluate the information.

Ken Tracton

# Contents

| 1 | Introduction to Microprocessors                                                                                                                                         |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | The TMS9900 Processor Chip                                                                                                                                              |

| 3 | TMS9900 Family Support Chips40<br>TMS9901 Programmable System Interface—TMS9902<br>Architecture—TMS9903 Synchronous Communication<br>Controller—TIM9904 Clock Generator |

| 4 | 9900 System Design                                                                                                                                                      |

| 5 | Hints About Peripherals                                                                                                                                                 |

|   | Appendix                                                                                                                                                                |

|   | Index95                                                                                                                                                                 |

## Introduction to Microprocessors

The first microprocessors were 4-bit types which handled data as 4-bit nybbles. The earliest of this new breed of machines, the Intel 4004, was a major breakthrough. It was quickly followed by the Intel 4040, and the National Semiconductor IMP-4.

The 4-bit microprocessors are, for the most part, considered obsolete. The exceptions are the one-chip microcomputers, with storage and interfaces, as well as control on a single chip. These are excellent controllers and have been used in such devices as sewing machines, CRT controllers, and TV games.

An example is the TMS1000-series microprocessor, made by Texas Instruments (TI), consisting of the TMS1000, TMS1100, TMS1200, and TMS1300 processors. These consist of one-chip microprocessors containing from 1024 to 2048 bytes of read only memory (ROM), a central processing unit (CPU), 32 to 64 bytes (addressed as 64 to 128 nybbles) of random access memory (RAM) for a scratch pad, and simple input/output (I/O) logic.

These chips are incredibly low in cost when one considers their power and versatility; with their various kin, they have completely changed the electronics and controller fields.

Although the Intel 4004 set the world on its ear, the first 8-bit units, of which the Intel 8008 is the most famous, turned it upside down.

The smallest minicomputer being taken seriously were 8-bit (1 byte) processors, and suddenly there was a complete computer on a chip.

In actuality these first 8-bit machines were bigger versions of the 4-bit types and meant to be used as controllers, not as computers. Their instruction set and interfacing requirements were oriented towards process control. Even so, the hobbyists started using them for other purposes and quickly started up that class of systems called microcomputers.

Microcomputers are now used in such sophisticated devices as (a) pocket computers, more powerful than the early monsters in the computer industry; (b) desk-top computers, capable of serving such, diverse users as car dealers and small motels and hotels; (c) office computers, for the accountant and business man; (d) TV games, of such sophistication that one of these units can play hundreds of different games, controlled by the insertion of a small tape cartridge, and (e) robots, capable of such far-ranging feats as controlling Mars and Jupiter probes to as mundane feats as delivering the office mail.

The number of 8-bit machines has grown enormously, and is always in flux, with newer models available almost daily. The following is a list of some of the better known 8-bit microprocessors:

- F8 by Fairchild

- 3870 by Mostek

- SC/MP by National Semiconductor

- 8080 family by Intel

- Z80 by Zilog

- 6800 family by Motorola

- 6500 family by MOS Technology

- 2650 family by Signetics

- COSMAC 1802 family by RCA

#### THE 12-BIT MICROPROCESSOR

This microprocessor is a lonely creature, standing by itself in terms of the number of variations available. The IM-6100 from Intersil duplicates the Digital Equipment Corp. (DEC) PDP-8 almost perfectly.

The PDP-8 has one enormous feature going for it that makes the soft-ware-compatible IM-6100 very popular and tempting, that is, the software of the PDP-8. It is this colossal amount of material that almost compensates for the primitive instruction set capability of the IM-6100.

In languages alone it outstrips any other microprocessor (as well as some much larger machines), having;

| A) DIBOL       | DEC business language                        |

|----------------|----------------------------------------------|

| B) ALGOL-60    | the subroutine definition language           |

| C) FORTRAN     | the most famous scientific language          |

| D) SNOBOL      | string manipulation language                 |

| E) APL         | the mathematical language                    |

| F) LISP        | the artificial intelligence language         |

| G) BASIC       | the most popular language of all             |

| H) FOCAL       | a supercalculator language                   |

| I) LIBRA .     | time-sharing FOCAL                           |

| J) MACRO       | a macro-assembler for machine language users |

| K) LINK-EDITOR | for hooking everything together              |

| L) DOS         | for developing systems                       |

| M) TSS         | time-sharing system                          |

If the PDP-8 or IM6100 has all this power, then why, you may ask, isn't this book written solely on the construction of this machine? The main reason is that I feel that the TI TMS9900 microprocessor is fresh ground for the microcomputer user, with even more potential than the PDP-8.

Other reasons include the most advanced architecture of any true microprocessor is currently within the TMS9900; the TMS9900 has the greatest flexibility of any microprocessor yet developed; the TMS9900 has the best instruction set of any microprocessor, exceeding many minicomputers; and the software development pace for the TMS9900 is increasing exponentially.

While there are so-called microprocessors with power just as great as the TMS9900 (the DEC LSI-11 includes floating point as an option) they are either not as cost-effective or not as flexible (e.g., the LSI-11 could never be used as economically to control a CRT or other smart devices). The LSI-11/2 now consists of separate CPU, memory, and interface cards, but the CPU is not available as a chip or chip group without the card.

#### THE 16-BIT MACHINES

Just as the 8-bit microprocessors absorbed and expanded the low end of the minicomputer industry, the 16-bit versions are begin-

ning to make themselves felt in the main stomping grounds of the minicomputer field.

The 16-bit unit, unlike its cousin the 8-bit type, is not really a microprocessor, but is in reality a minicomputer using large-scale integration (LSI) technology. The main 16-bit machines are;

- 9440 by Fairchild

- MicroNOVA by Data General

- CP1600 by General Instruments

- Pace by National Semiconductor

- TMS9900 family by Texas Instruments

- MC2 by Hewlett-Packard

- LSI-11 by DEC

The Fairchild 9440 is an exact duplicate, in terms of instruction set, of the Data General NOVA, while the Data General microNOVA is an extended version of the same machine, with built-in stack and hardware multiply and divide.

The DEC LSI-11 is an LSI version of their PDP-11 minicomputers.

The NOVA was designed as a 16-bit version of the 12-bit PDP-8 with added capabilities that eliminated some of the limitations inherent in the PDP-8. This does not mean that the instructions were simply expanded, but that the concept was expanded.

From this we can see that the IM6100, the 9440, the microNOVA, and the LSI-11 are all minicomputers in the guise of microprocessors.

Although the other 16-bit machines may have much to recommend them, they are not felt by myself to be as desirable.

This book is oriented towards the person wishing to construct a machine and not simply buy a completed unit. For instance, Hewlett-Packard MC2 is used by Hewlett-Packard and is not, at this time, available to anyone else.

The LSI-11 is a multichip system, already designed, and is not available as a separate chip set. This makes sense if we remember that it is meant to duplicate a PDP-11 as a whole and variations would defeat the original design purposes.

Although the 9440 and the microNOVA are available as separate chips and chip sets, they are meant to exactly duplicate the NOVA system by Data General.

#### WHY THE 9900?

The TI 9900 was chosen for this book for several reasons; it is an LSI minicomputer rather than a microcomputer chip (microprocessor) in the usual sense of the word. This means that, for the hobbyist or professional, the instruction set and architecture are simple and clean, with little to interfere with designing hardware or software.

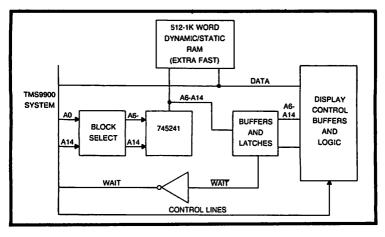

The minimum system (see Chapter 4 for a block diagram) is not significantly more expensive than a minimum system using other processors, and may even be less expensive, particularly when compared to other 16-bit processors.

The 9900 is a 16-bit machine with byte addressing and a general register bank (16 registers); it is a 64-pin chip with separate lines for data and addresses, making complex interfaces unnecessary; and it does not require the use of complex memory systems to operate, allowing easy mixing of different memories.

The family of 9900 chips is complete, allowing powerful systems to be designed with ease. There exists currently a version of the TMS9900, called the TMS9980, which can use 8-bit modules and is totally software compatible with the 9900.

The 9900, while still young in terms of software, has most of the key software already available, such as:

- 1) COBAL-full ANSI COBOL compiler

- 2) FORTRAN-a re-entrant, full ANSI/ISO compiler

- 3) A real-time multiprogramming, time-sharing operating system with all the bells and whistles.

- 4) BASIC-A time-sharing BASIC

The 9900 is available as a one-card computer called the 990/4, as a one-card computer with on-board RAM and ROM called the 990-100M, a TTL version with memory mapping to two-million bytes, called the 990/10. There also exists an  $I^2L$  version, with higher speed and pin compatibility termed the IBP-9900. There is the 9980 (8-bit compatible) version of the 990-100M called the 990-180M. And of course the TMS9900, TMS9980, and the IBP9900 are all available as separate chips, along with the rest of the family chips.

All in all I feel that the TMS9900 (or the IBP9900), as a personal computer, is an excellent choice.

#### WHAT IS IN THIS BOOK

The 9900 chip itself is obviously covered in detail, since this is the central processing unit, the very nucleus of the computer system.

The 9901 is a programmable systems interface, which provides the 9900 with an interval timer, an event timer, up to 16 I/O ports, and up to 15 interrupt input lines.

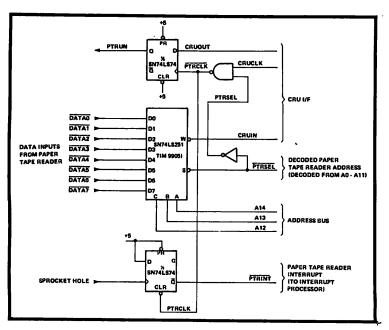

The 9902 is an asynchronous communication controller (ACC), which allows interfacing the 9900 to such devices as teletypewriters of all kinds, CRT terminals, hard-copy terminals, paper tape readers, and punches and cassette tape interfaces.

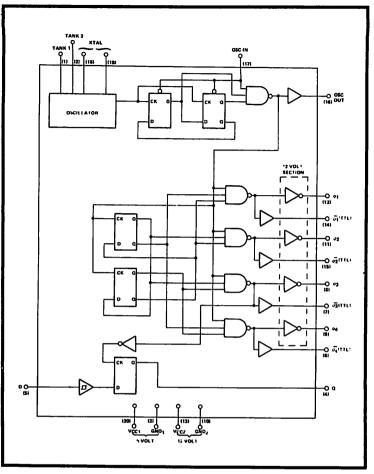

The 9904 is a clock generator which generates all the synchronization signals for the 9900, the 9901, etc.

The 9903 is a synchronous communication controller which eliminates the need for software for the protocols, such as binary synchronous (often called bi-synch), synchronous data link control (usually SDLC), and almost all other synchronous protocols, with the link synchronization and control handled by this chip, the 9903.

## The TMS9900 2 Processor Chip

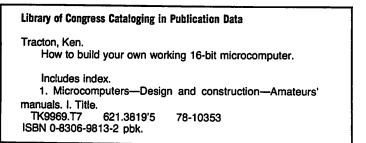

The TMS9900 is a single IC in a 64-pin dual inline package. This package (Fig. 2-1) is larger than the more familiar 8-bit microprocessor chips. The 9900 is 3.2 inches long, and the two rows of pins are 0.900 inch apart rather than the 0.600 inch spacing used in 40-pin packages. Adjacent pin spacing is the familiar 0.010 inch. Pin number 1 is identified by an index dot between Pins 1 and 2.

The chip is produced by N-channel silicon-gate MOS technology, and requires three power supplies for its operation. The recommended levels for these supplies are -5, +5, and +12 VDC. Under typical conditions, the chip draws 50 ma from the +5 VDC supply 75 ma is rated maximum), 100 microamps from the -5 VDC rail 1 ma maximum), and 25 ma from the +12 VDC source (45 ma maximum).

All signal levels (except for the four clock signals), both input and output, are compatible with TTL logic. The clock signals must not be lower than +3 V at their positive points, and TTL guarantees only a +2.4-volt level for a HI signal. If the recommended TIM9904 clock chip is used to provide the clock signals you will have no problem; TTL normally provides adequate drive, but this is not guaranteed.

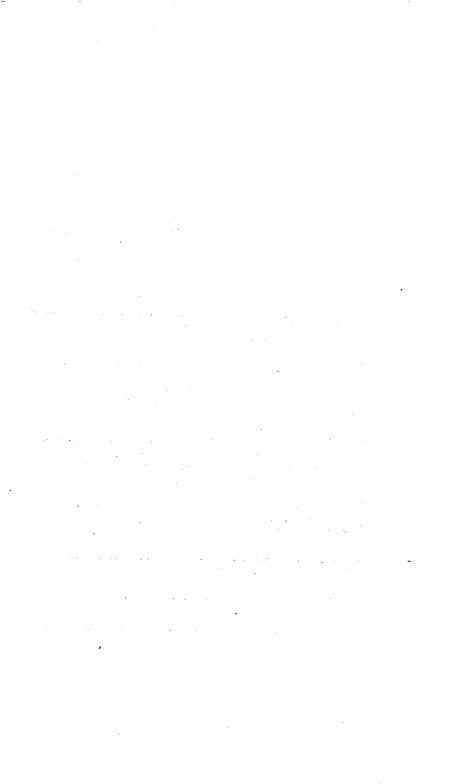

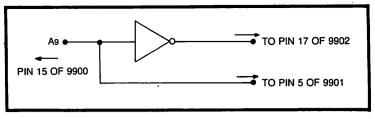

Maximum clock frequency is 3 MHz, and four non-overlapping phases must be supplied. The 9904 circuit uses a 48-MHz crystal, or a 12-MHz external oscillator, to provide these requirements. Fig.

Fig. 2-1. The 64-pin dual inline package of the TMS9900 is larger than the more familiar 40-pin DIP configuration used by 8-bit microprocessors. Added 24 pins make possible more system interconnections. (Courtesy of Texas Instruments)

2-2 shows clock signal timing requirements. The times shown are for maximum-frequency operation. For operation at slower speeds, the duration of individual phases may be extended but the 5-ns guard times between signals should remain unchanged.

Input lines to the TMS9900 all have high impedance to minimize loading on signal sources. Outputs are all capable of driving two

Fig. 2-2. Clock waveforms required by TMS9900 when operating at maximum 3-MHz frequency are shown here. Dead space of 5 ns between phases is essential to proper operation of processor. (Courtesy of Texas Instruments)

standard TTL inputs each, and no pull-up resistors are necessary. Most standard memory devices can be connected directly to the 9900 without intervening buffers. If an external circuit imposes more than the equivalent of two TTL loads (that is, requires more than 3.2 ma of driving signal), buffering is required.

| TMS 9900 PIN ASSIGNMENTS                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VBB 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 64       HOLD         63       MEMEN         62       READY         61       WE         60       CRUCLK         59       VCC         58       NC         57       NC         56       D15         55       D14         54       D13         55       D14         56       D15         57       NC         58       D12         52       D11         51       D10         50       D9         49       D8         448       D7         446       D5         446       D4         443       D2         444       D3         443       D2         444       D3         445       D4         440       VSS         39       NC         38       NC         38       IC1         34       IC2         33       IC3 |  |  |

Fig. 2-3. Pin connections for processor chip are grouped by function to simplify PWA card layout. (Courtesy of Texas Instruments)

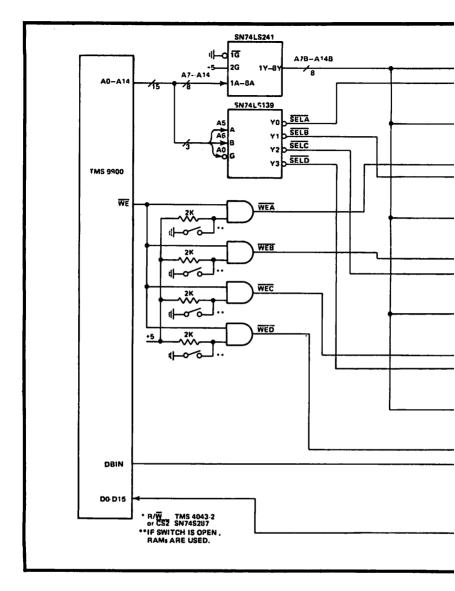

Pin assignments of the TMS9900 (Fig. 2-3) were made to simplify the layout of a circuit board, by grouping related signals into sets and assigning each set to adjacent pins. Thus all signals of the data bus are together, and so forth. This permits shorter conductor runs and more compact circuit board layout.

Pay close attention to these critical points in layout:

The clock inputs must be located as close as possible to the clock driver circuit, because these signals have fast rise and fall times while driving relatively high capacitance through a wide voltage swing.

The 12-volt supply to the clock drivers should be decoupled with both large (15-uf minimum) and small (0.05-uf maximum) capacitors in order to remove both low-frequency and highfrequency transients from the supply lines.

All power inputs must be decoupled as close to the chip as possible. The +5 VDC power drain can vary by nearly 100 ma over a 20-ns interval, if all data and address lines simultaneously switch to low level, and the resulting spike can interfere with system operation unless decoupled at the 9900 socket.

#### DATA AND ADDRESS ORGANIZATION

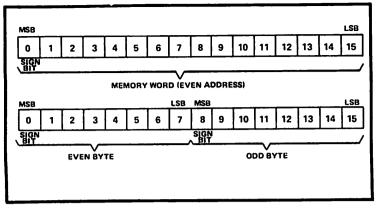

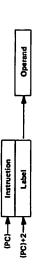

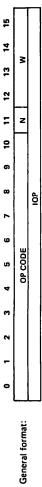

The TMS9900 uses a 16-bit memory word and 16-bit addresses. The 16 bits of the memory word (Fig. 2-4) are referred to as DO through D15, with D0 being the most significant (leftmost) bit and D15 being the least significant. Similarly, the 16 bits of an address are referred to as A0 through A15, with A0 being most significant.

Each memory word can be considered as being made up of two 8-bit bytes. In this case, D0 through D7 form one byte, and D8 through D15 form the other. Most data operations can be performed on either words or bytes, depending upon a flag bit in the operation command code.

The 16-bit memory addresses actually refer to bytes rather than to words. Only 15 of the 16 address bits are brought out to external address lines; A15 is used only inside the chip, to signify to a byte operation which of the two bytes is to be affected. When A15 is 0, the byte composed of D0 through D7 is addressed; when A15 is 1, the affected byte is D8 through D15.

Since only 15 address bits are available externally, all memory addresses involve full 16-bit words, and are on even-byte boundaries. That is, memory location 0001 does not exist; the system

Fig. 2-4. Bit designations which memory word are as shown at top here. Bytes of word are as shown below. (Courtesy of Texas Instruments)

steps from 0000 to 0002, then to 0004, and so forth. Thus the memory space directly addressible is 32,768 words, and any memory transfer moves a full 16-bit word regardless of whether one or both its bytes are to be modified.

#### INTERNAL ORGANIZATION

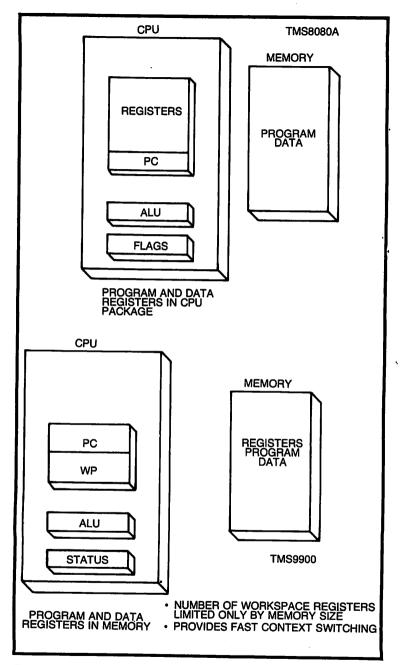

The advanced memory-to-memory architecture of the TMS9900 is best described by comparing it to the more conventional register-oriented design exemplified by the popular 8080 microp-rocessor. Such a chip (Fig. 2-5) contains a number of registers, a program counter, an arithmetic and logic unit (ALU), and a set of status flags. Data may be transferred from register to register, or between register and memory. Most arithmetic and logic operations involve a special register (the accumulator) and either another register, immediate data, or a memory byte.

For controller applications, this is adequate. The control parameters may be kept in the internal registers, and little communication with memory is required for data transfer.

However, when interrupt-driven input-output techniques are employed (which means most of the time, in information processing applications), all of the internal registers must be saved each time an interrupt occurs. Subsequently, at the end of the interrupt service routine, the registers must be restored. This continual saving and restoration of the registers may occupy as much processor time and program space as the interrupt service routine itself.

Fig. 2-5. Difference between TMS9900 organization (right) and more conventional approach of 8080 (left) is key to 9900's capability for rapid context switching. (Courtesy of Texas Instruments)

The TMS9900's memory-to-memory design differs in that only three registers are actually contained within the chip, and all three of these are automatically saved or restored as required by single program instructions or interrupt responses. The saving or restoring is called a "context switch."

The three actual registers in the TMS9900 (Fig. 2-5) are the program counter, the status register, and the workspace pointer. The first two of these correspond to their counterparts in the more conventional design; the third is the key to the advantages of the TMS9900.

In addition to the three actual registers, the TMS9900 employs 16 additional "workspace registers." These registers, identified as WR0 through WR15, may be used for the same purposes as any of the additional data registers of the more conventional architecture (with several exceptions). That is, any of the registers may be used as an accumulator or as an address pointer.

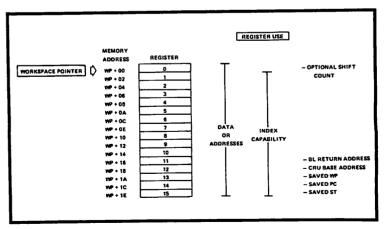

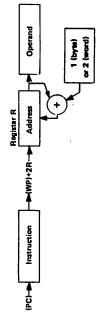

The 16 workspace registers (Fig. 2-6) may be located anywhere in memory, and you can have as many sets of them as you like. The only requirements are that the 16 register words in one set be in consecutively addressed locations, and that they not be in read-only memory.

The workspace pointer register points to WR0 in the currently active set of workspace registers; this gives the processor access to all 16 of the registers in the set.

Fig. 2-6. The 16 registers of the 9900 are organized as shown here. All addresses are relative to the workspace pointer. As many sets of registers as desired can be defined. (Courtesy of Texas Instruments)

Of the 16 workspace registers, 10 are available for any application. Three are dedicated to the context-switching operations, but their content may be used or changed by the same commands which apply to the 10 general-usage registers. The remaining three have special uses in certain commands, but again can be changed or used like any other workspace register (with one exception).

Registers WR1 through WR10 are the general-usage registers. Each can be used as an accumulator, a memory pointer, or an index register, depending upon specific bits in the command used to address the register.

The other registers can also be used as accumulators, memory pointers, and (except for WR0) as index registers. Indexing involving WR0 is not allowed.

The registers dedicated to context switching are WR13, WR14, and WR15. When a context switch occurs, the old content of the workspace pointer is stored in WR13 of the new workspace, the old program counter in WR14, and the current content of the status register in WR15. If these three registers are not modified by the program, the context switch can be reversed by reloading WP, PC, and ST from WR13, WR14, and WR15 respectively. This is done by a single command, Return Workspace (RTWP).

Special uses of the remaining registers are as follows: WR0 contains an optional shift count used by all four shift instructions. WR11 contains the return address stored automatically by the Branch and Link (BL) command, which can be used to call a subroutine without performing a context switch. To return from the subroutine a Branch using WR11 (B 11) is executed. WR12 contains the bit base address for communication-register unit (CRU) operations.

In addition to the workspace-register feature, the memoryto-memory organization of the 9900 has another unusual result. Arithmetic and logical operations are not limited to actions involving the registers; any memory location can be altered, without the need for moving its content into a register to make the change, then moving it back after the change is complete. That is to say, any memory location—not just the workspace registers—can be used as an accumulator, merely by addressing it appropriately in the command.

At first glance, it might appear that this architecture would result in an inordinate number of memory accesses in order to accomplish any program action. In fact, the number of accesses is not significantly larger than with the more conventional registeroriented microprocessor designs, since they too must perform at least one memory access per program instruction in order to fetch the instruction for execution. By reducing the number of program steps which must be accessed, the 9900's design permits more data accesses without penalty.

#### **CONTEXT SWITCHING**

The process of switching from one set of registers to another, by switching the pointer to the workspace, is known as context switching. A context switch is performed when the LOAD signal goes low, immediately after the RESET signal returns to high level after being low, when any of the 15 maskable interrupts is recognized and allowed, whenever one of the 16 possible Extended Operation (XOP) commands is executed, whenever a Branch and Load Workspace Pointer (BLWP) command is executed, or when the Return Workspace (RTWP) is executed.

All of these context switches, except that resulting from executing RTWP, are performed in the same manner once the necessity for the context switch is established. External signal lines LOAD and RESET establish the need for their context switches. An allowable interrupt similarly establishes its need. Context switches required by command execution are established by fetching and decoding the command.

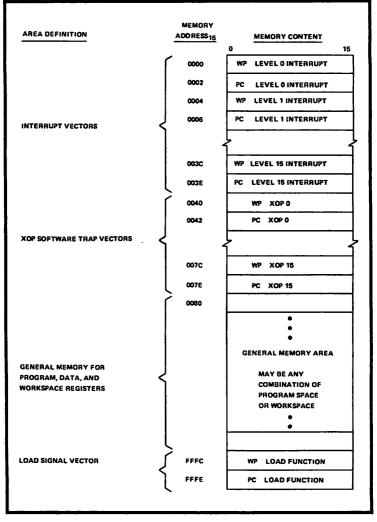

Once the need for a context switch is known, the existing workspace pointer and status register are temporarily saved and a new workspace pointer value is obtained from an appropriate memory location. For all context switches except BLWP and RTWP, the location of the new workspace pointer value is built into the 9900 chip (Fig. 2-7). For LOAD the new value is at memory location FFFC (16). For RESET, it is at 0000. For Interrupt 1, it is at 0004, and so forth for the higher-numbered interrupts up to Interrupt 15, at 003C (60 decimal, or 4 times 15). The values for XOP immediately follow those for the interrupts, at memory locations 0040 (XOP 0) through 007C (XOP 15). The value, once obtained, is loaded into the workspace pointer register, which instantly changes the entire program context to reflect the new workspace.

With the new workspace established, the saved value of the status register is stored in new WR15. The content of the program

counter register, which has not yet changed, is stored in new WR14. The saved value of the old workspace pointer is stored in WR13, and finally the new value of the program counter is read from the memory location immediately following that from which the new workspace pointer was obtained (FFFE for LOAD, 0002 for RE-SET, and so forth). Program execution then continues, using the new value of the program counter and the new workspace.

After any of these context switches is accomplished, the first instruction (that addressed by the new program counter) will be executed before any interrupt will be recognized. This permits the interrupt facility to be locked out when desired.

Because the old WP, PC, and ST are pushed into WR13, WR14, and WR15 of the new workspace, it is possible to restore them and thus to restore the exact internal system conditions which existed at the instant the context switch was performed. This is functionally the equivalent of the stack push and pop (or pull) sequences employed by many 8-bit microprocessors. The 9900, however, does everything by a single instruction, rather than requiring an instruction sequence.

Restoring the previously used workspace, PC, and status is accomplished by the RTWP instruction. Its action may also be considered a context switch, but in the reverse direction. The RTWP action is never performed automatically; it always results from the program's fetching and decoding the RTWP command.

When the RTWP command is decoded, the processor fetches the old status from WR15 and stores it in the status register. Next, it restores the program counter from WR14. Then it restores the workspace pointer from WR13. Note that the values of ST, PC, and WP which existed when the command was decoded have been lost; none of them are necessary any longer. Finally, the restored program counter content is loaded onto the memory address lines and the next instruction is taken from the location thus addressed. Unlike the other context switches, the interrupt facility remains active when RTWP is executed (unless disabled by the restored interrupt mask in the status register).

#### **INTERRUPTS**

The TMS9900 provides 16 interrupts, together with LOAD and RESET pins. Interrupt 0 and RESET accomplish the same actions.

Fig. 2-7. Memory locations 0000 through 007E, plus FFFC and FFFE, are dedicated to special uses as shown in this memory map. All other addresses are free for general use. (Courtesy of TI)

Interrupt priority is established by the number of the interrupt. Interrupt 15 has lowest priority, and Interrupt 0 or RESET the highest. Interrupt 0 cannot be masked; the remaining 15 are automatically masked in such a way that no interrupt of lower priority will be accepted while any interrupt is being serviced.

The interrupt system uses five lines. One, INTREQ, signals the TMS9900 that an interrupt is requested. This line is normally

high, and goes low to signal an interrupt request. The other four, IC0 through IC3, form a 4-bit binary code which indicates the level of the interrupt request. IC0 is the most significant, and IC3 the least significant, bit of the code, and a high level indicates a "1" bit. Thus, LLLH on IC0-IC3 (in that sequence) indicates 0001, or Interrupt 1.

When an interrupt request is recognized on the INTREQ line, the TMS9900 compares the interrupt code on ICO-IC3 with the interrupt mask contained in status-register bits ST12 through ST15. If the interrupt code is less than or equal to the mask (indicating a higher or equal priority interrupt), the interrupt is allowed and a context switch is performed after the currently executing instruction has been completed. After the context switch, the interrupt mask is automatically reduced by one so that no other interrupt of equal or lower priority can be allowed.

When the interrupt mask is equal to zero (bits ST12 through ST15 all zero), no requested interrupt can be of higher priority, and only the RESET interrupt can be equal. Thus all interrupts except Interrupt 0 (RESET) can be disabled by forcing the interrupt mask to zero. One command, Load Interrupt Mask Immediate (LIMI), permits the interrupt mask to be set to any value, and the first command after any context switch will be executed before interrupts will be examined again. Thus by making the first command of a critical routine a LIMI 0, that routine can turn off interrupt action. When the routine is finished and control passes back to the interrupted action via the RTWP command, the previous interrupt mask is restored along with the other 12 bits of the status register, and interrupts are once again enabled.

This approach to interrupt control makes priority determination almost automatic. Each external circuit which can produce an interrupt request must also provide its interrupt code on lines IC0 through IC3. If each device has a separate code, no additional hardware is necessary to determine which device requires service or if response is permissible. Most systems can operate with no more than 15 different interrupts. Should more prove necessary, several devices can be assigned the same code and the interrupt service routine can then interrogate all of them to determine which requires service. Alternatively, external hardware can be added to sort out priorities so that the 9900 sees only one of 15 requests, but each request could have originated from any of several different circuits.

#### **INPUT/OUTPUT TECHNIQUES**

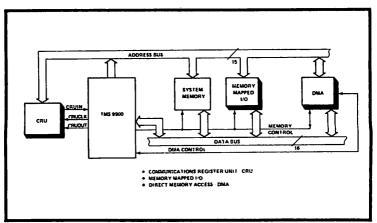

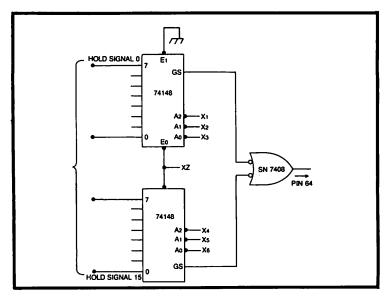

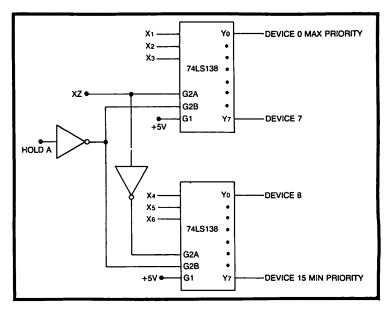

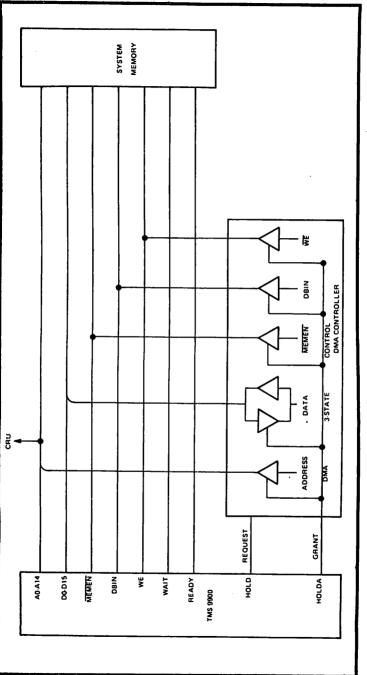

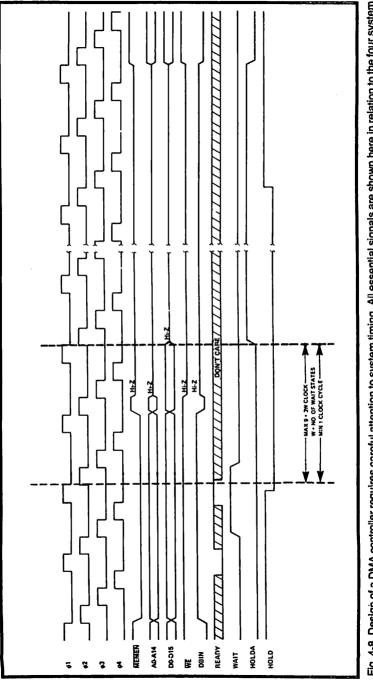

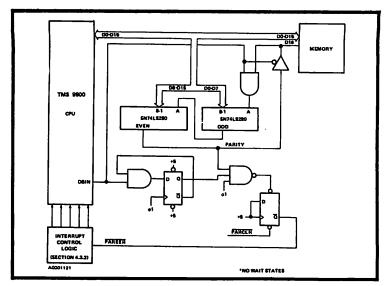

Any or all of three widely different techniques may be used for input/output data transfers between the TMS9900 processor and memory on one side, and the external world on the other. The three techniques (Fig. 2-8) are direct memory access (DMA), memorymapped I/O, and the communications-register unit (CRU) capability.

DMA provides direct transfer of data between the peripheral devices and memory, without involving the processor at all (except to guarantee that the processor does not attempt to access memory at the same time). With many processors, this is the cleanest way to transfer data, but it always requires some external hardware to control the DMA activity and to assure that both the processor and the peripheral device wait their proper turns for memory access. Because of its complexity, DMA I/O is outside the scope of this volume.

Memory-mapped I/O assigns memory addresses to the various peripheral ports, and "reads" from or "writes" to the peripheral port just as though it were actual memory. This approach makes at least one memory location per peripheral device unavailable for actual data storage, but nevertheless is a popular technique. Several 8-bit microprocessors (notably, the 6500 and 6800 families) use memory-mapped I/O to meet all their requirements. Again, memory-mapped I/O is outside the scope of this volume, because

Fig. 2-8. These three types of input/output techniques may be used with the 9900. Only the CRU capability is unique to the 9900. (Courtesy of Texas Instruments)

the technique used depends entirely upon the specific peripheral involved.

The final technique, the CRU capability, is unique to the TMS9900 family and is an extension of the idea used for direct accumulator I/O in such processors as the 8080.

A communications register unit is defined in the 9900 system as any external unit making use of the processor's CRU capability. This capability takes the form of three dedicated I/O pins (CRUIN, CRUOUT, and CRUCLK), 12 bits (A3 through A13) of the address bus, and five processor instructions which permit the program to set, reset, or test any of 4096 addressable bits in the external device, and to move data between memory and CRU data fields.

While the capability provides 12 bits of CRU address, making it possible to uniquely address up to 4096 bits in the CRU, any specific device used as a CRU need not have all these bits present. A single-bit device such as a flip-flop could be used as a CRU. In a more practical vein, the TMS9901, 9902, and 9903 peripherals are all intended to be used as CRU's. If you prefer, any type of peripheral controller can be turned into a CRU by providing the proper interface to make it compatible with the 9900's CRU-oriented commands and bit addressing.

#### **CRU INTERFACING**

The CRU interface is a dedicated serial I/O capability which permits transfer of from 1 to 16 bits at a time. Since bits are individually addressed, no masking instructions are necessary in I/O service programs, and I/O fields need not be identical in size to the memory word (but must be no longer than 16 bits).

CRU interface signals from the TMS9900 consist of (1) the CRU clock (CRUCLK, pin 60) which, when high, means that the 15 address lines contain either an externally decoded operation (if A0, A1, or A2 is high) or a bit address in the CRU (if A0, A1, and A2 are all low); (2) CRUOUT (pin 30) which contains the bit being output; and (3) CRUIN (pin 31) which contains the bit being input.

The CRU can be considered to be a pair of addressable memories of 4096 bits each (one memory for input, and one for output). Five instructions access the CRU. They are:

• Test Bit (TB), which allows reading any single bit in the CRU;

- · Set Bit to One (SBO) and

- Set Bit to Zero (SBZ), which allow altering one bit in the CRU; and

- · Load Communications Register (LDCR) and

- Store Communications Register (STCR), which allow altering or reading up to 16 bits at a time via a multi-bit CRU data transfer.

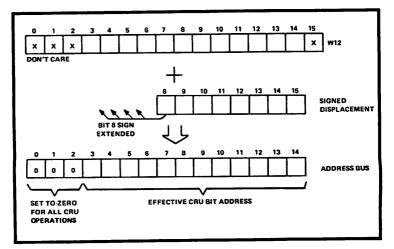

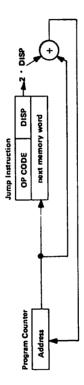

Each of these five instructions first causes the address of a single bit in the CRU address space to be formed as shown in Fig. 2-9 by adding a displacement value (contained in the instruction) to the CRU base address (contained in WR12), then places the resulting bit address on address lines A3 through A14 while forcing A0, A1, and A2 to 000. The bit appears on either CRUIN (for TB or STCR) or CRUOUT (for SBO, SBZ, or LDCR), strobed by CRUCLK.

The three single-bit commands operate explicitly; TB places the received bit value into ST2, where it may be tested by a subsequent JEQ or JNE command. If the bit value was 1, the EQUAL condition is set. SBO and SBZ set the CRU bit to 1 and 0, respectively.

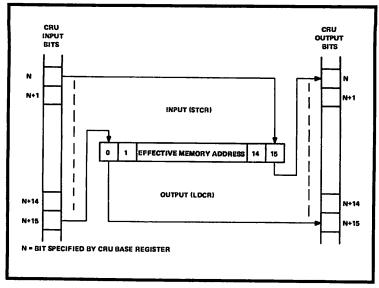

Only one bit per machine cycle is processed by any of the CRU commands. Multi-bit commands LDCR and STCR perform as many cycles as necessary to transfer the specified number of bits, chang-

Fig. 2-9. The CRU address placed on the address bus (bottom) is developed by adding an 8-bit signed displacement contained in the I/O command itself (center) to the CRU base address held in workspace register 12 (top). This operation is repeated for each addressed bit. (Courtesy of Texas Instruments)

Fig. 2-10. Multi-bit CRU data transfers by the LDCR and STCR commands operate as shown here. On input (STCR), the bit having the lowest CRU address moves into the rightmost bit of the addressed memory word. On output (LDCR), similarly, the rightmost bit goes to the lowest CRU address. (Courtesy of Texas Instruments)

ing the bit address after each cycle. Each bit is moved between processor and CRU as shown in Fig. 2-10.

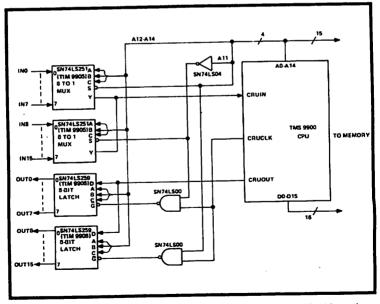

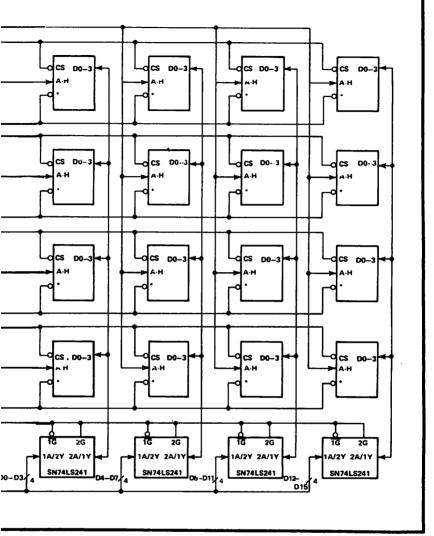

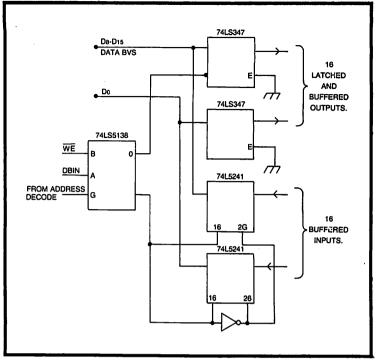

The 16-bit CRU shown in Fig. 2-11 illustrates the basic principles involved in CRU interfacing. Note that address lines A0 through A10 are ignored by this circuit; it will interpret any of the external commands as a CRU action, and each of its 16 input and output bits has 256 possible addresses. That is, input bit IN0 and output bit OUT0 can be addressed as CRU bit 0, bit 16, bit 32, and so forth up to bit 4080. Whenever address lines A11 through A14 contain the 0000 pattern, IN0 and OUT0 are addressed.

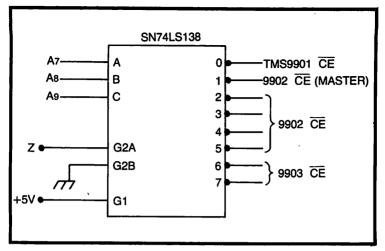

The TMS9901, 9902, and 9903 support chips (discussed in detail in Chapter 3) are designed for use with the CRU interface. Each of them has only 5 address-line inputs, so each chip occupies 32 bits of the 4096-bit CRU memory space. Each of these chips also has a Chip Enable (CE) input to permit the other seven address lines to select one of several chips in a system.

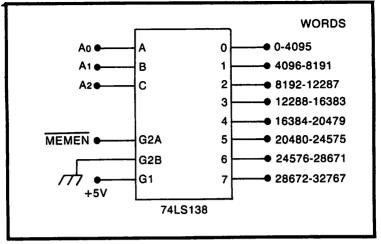

If only one CRU device is to be used, the multiple-address approach (simply grounding the CE line) would be enough. However, let us suppose that we wish to connect 8 devices on the CRU interface. We can divide the CRU address signal as follows;

- 9901 for interrupts and interval timer, addressesd as bits 0-31

- 2) 9902 for master terminal, addresses 32-63

- 3) Four 9902s for remote terminals, modems, addresses

64-95 96-127

128-159

160-191

- 4) 9903 for a BI-SYNC terminal addresses 192-223

- 5) 9903 for an SDLC terminal addresses 224-255

The circuit as shown in Fig. 2-12 would be used. This circuit uses an 74LS138 3-to-8 decoder. Line Z comes from the CRU clock.

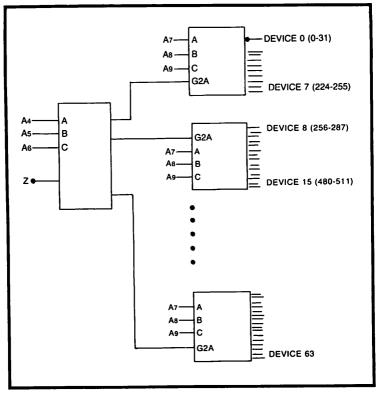

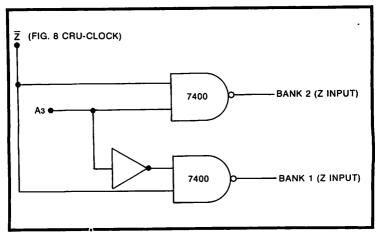

Should we wish to further expand the system, we could use Fig. 2-13 to increase the number of circuits to 64. This requires 9 74LS138 decoders. Figure 2-14 shows decoding for your system up to 128 devices, allowing up to 127 terminals to be connected to such a system. This circuit requires 36 74LS138 decoders and some TTL circuitry.

Fig. 2-11. This 16-bit CRU can be constructed with only 5 IC chips, since one-quarter of a 74LS00 can be used instead of the 74LS04. It may be adequate for small systems. (Courtesy of Texas Instruments)

Fig. 2-12. This 3-to-8 decoder can be used to select one of eight CRU devices.

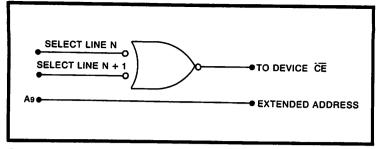

Should a chip require the use of more than 32 bits of the CRU, Fig. 2-15 shows a technique to tie two select lines together. By tying two lines together we allow up to 64 CRU bits to be addressed as a group. To split a 32 bit group into two 16 bit groups, use Fig. 2-16.

So far we have seen how to split the CRU address lines into:

- A) 8 32-bit lines (Fig. 2-12)

- B) 16 32-bit lines (Figs. 2-12 and 2-14)

- C) 64 32-bit lines (Fig. 2-13)

- D) 128 32-bit lines (Figs. 2-13 and 2-14)

- E) recombined 64-bit lines (Fig. 2-15)

- F) split-pair 16-bit lines (Fig. 2-16)

There are, of course, other ways to achieve some of these results. One way is to use a 4-to-16 decoder. This would allow the combination of Fig. 2-14 plus two circuits from Fig. 2-12 to be replaced by one circuit.

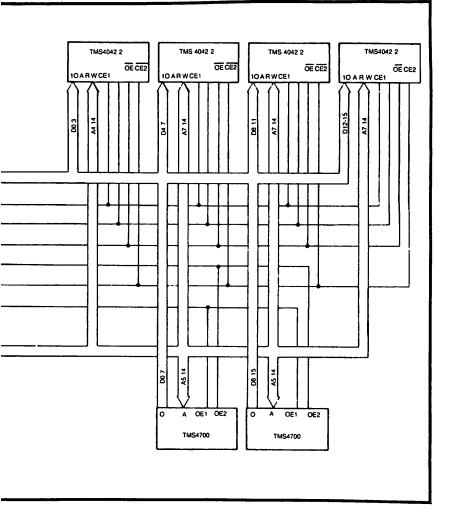

#### **MEMORY BANK SELECTION**

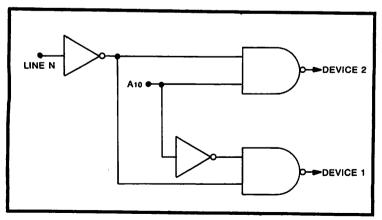

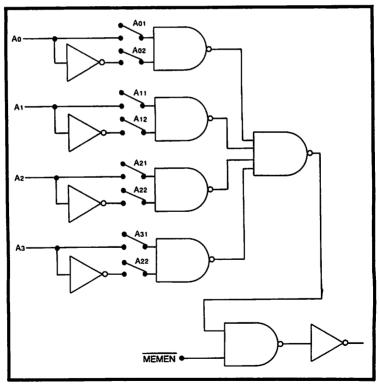

Memory system design presents the same address-mapping problem as the CRU. Should you wish to select a section of memory you would have several choices open to you:

• Select logic as shown in Fig. 2-17 will allow selecting any group of 4K words of storage, up to the maximum of 32K words.

Fig. 2-13. By increasing the number of decoders to 9, we can handle up to 64 different devices.

Fig. 2-14. For a maximum system we can use this circuit with 36 decoders and associated logic to select one of 128 CRU devices.

Fig. 2-15. Two select lines can be tied together with this circuit if the need arises.

• The use of a 4-to-16 decoder will allow using address lines A0 through A3 to decode in groups of 2K words (4K bytes), up to a maximum of 32K words (64K bytes).

Several problems immediately arise from the use of this technique.

- What happens if we require an address boundary of 1K for a 4K range?

- The number of lines can get very cumbersome indeed.

- There are times when we wish to address as few as 2 words on the memory line (or memory mapped I/O).

These problems can be solved by circuits such as shown in Fig. 2-18. This circuit can be set to select any 2K word boundary. Adding an extra section would allow us to select any 1k word boundary. As an example: closing switches A01, A12, A21 and A31 would cause selection of addresses in the range 22528 thru 24575 inclusive.

Fig. 2-16. This circuit can split a 32-bit group into two 16-bit groups.

Fig. 2-17. A 3-to-8 decoder allows selection of any single 4K-word block of memory, up to the maximum 32K of a 9900 system.

Fig. 2-18. This circuit can be used to select memory on any 2K boundary rather than the 4K boundaries offered by Fig. 2-17.

Such a circuit can be implemented with standard logic, with the switches replaced by jumpers or plugs.

The circuit can be expanded to almost any level and requires access only to the address lines and the memen line.

Using this approach, we can build modules of memory, selecting the addresses when connecting these modules together. Note that we have just started the first section of the DMA requirement. The modules would no longer depend on the 9900 for addresses, but would depend only on the contents of the address (and data) lines, which could be generated by other devices.

In fact, except for the 1K boundary with 4K memory problems, we have solved the addressing problems. The 1K boundary problem and others of that nature can be solved with more complex versions of Fig. 2-18.

For CRU utilization it is recommended that the multiline decoder approach be used, since these devices are more closely tied to the processor.

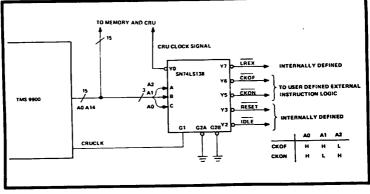

# EXTERNAL INSTRUCTIONS AND STATUS DISPLAY

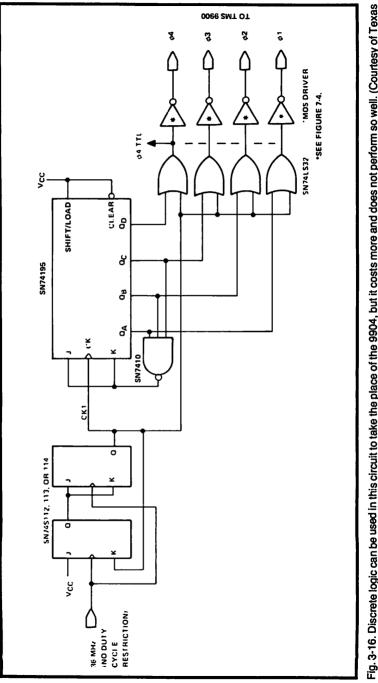

From the discussion of the CRU, we learned that when any of address lines A0 through A2 was active together with the CRUCLK signal, an operation code has been detected which requires external decoding and processing. Figure 2-19 shows a circuit which will decode the address lines (see Fig. 2-20) and CRUCLK line. Note that the IDLE instruction is the only one of these operations to actually be processed by the 9900 itself.

The other instructions are used in the 990, but might be used in your system for such purposes as control of interval timers, control of a floating point processor, control of an array processor, or a Fast-Fourier Transform processor. They can be used to control a memory mapping circuit to extend the capacity of the 9900, to address storage, or for interprocessor communication when building a multiprocessor system.

Pin 7 on the 9900 is also useful in the detection of instructions being executed, since when it is active the address lines contain the address from which an instruction is being fetched and the data lines contain the instruction itself. The data lines can be checked, and special instructions could be externally executed or the instruction could force an interrupt.

Fig. 2-19. The external instruction decode logic shown here makes it possible to use customized instructions, and also offers insurance against faulty CRU operation. (Courtesy of Texas Instruments)

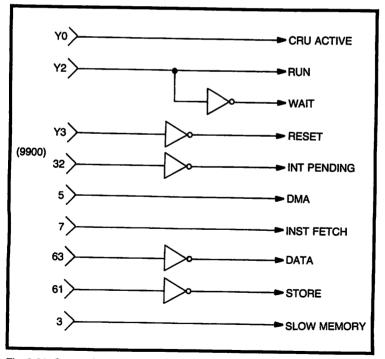

The designer could force new instructions (such as floating point or decimal instructions) into the machine by the use of memory waits and external execution. Designing such an extension is outside the scope of this book. However I can show you an excellent use for these signals as indicators of the processor state at any time. The following pins are probed on the processor and related circuits:

- The IDLE and RESET signals from Fig. 2-19 as well as the output CRU clock signal. These are pins Y2, Y3, and Y0 respectively on the SN74LS138.

- Pins 7, 61 (write enable), and 63 (memory enable) on the 9900.

The resultant pinout of Fig. 2-21 can be connected to an LED readout to produce a front panel showing processor status. Note that pins 32, 5, and 3 of the 9900 are also shown. The basic reasons for connecting these additional pins to an indicator are:

**Pin 32.** This output Fig. 2-9, under typical conditions, would usually result in a very brief, almost invisible flash of light. However, it is possible for a more visible indication to occur as follows:

- 1. Looping in an interrupt routine would mean that the lower priority interrupts are being held, and the light would remain on. See Fig. 2-22 for a list of interrupt priorities.

- 2. Heavy interrupt rates can cause stacking of the interrupts and result in a visual indication of the interrupt rate. The brighter the light, the higher the rate.

| EXTERNAL INSTRUCTION | A0 | A1 | A2 |

|----------------------|----|----|----|

| LREX                 | н  | н  | н  |

| CKOF                 | н  | н  | L  |

| CKON                 | н  | L  | н  |

| RSET                 | L  | н  | н  |

| IDLE                 | L  | н  |    |

Fig. 2-20. Bit patterns on address lines A0, A1, and A2 for the five external instructions are shown here. (Courtesy of Texas Instruments)

Pin 5 means that the 9900 has lifted off the address and data buses and is allowing another device to access memory. A visual indicator would show how much of the time (by brightness) is being used by external devices on the line.

**Pin 3** would have meaning, if probed with a lamp indicator, only if mixed speed memories were used. Whenever this pin is active, the TMS9900 must wait for memory. The brightness of the lamp would indicate when a slow section of storage was being accessed.

Fig. 2-21. Connecting indicators as shown here provides an informative frontpanel display for a 9900 system. See text for full use of the information displayed.

|                       | Vector Location |                   | Interrupt mask values 10     |              |

|-----------------------|-----------------|-------------------|------------------------------|--------------|

| Interrupt Level       | (Memory Address | Device Assignment | Enable Respective Interrupts | Codes        |

|                       | In Hex)         |                   | (ST12 thru ST15)             | ICO thru IC3 |

| (Hinhaet nriority) 0  | 8               | Reset             | 0 through F*                 | 0000         |

|                       | 8               | External device   | 1 through F                  | 000          |

| . 0                   | 8               |                   | 2 through F                  | 0010         |

|                       | 0               |                   | 3 through F                  | 0011         |

| . 4                   | 10              |                   | 4 through F                  | 0100         |

| ·Ľ                    | 14              |                   | 5 through F                  | 0101         |

| , w                   | . 81            |                   | 6 through F                  | 0110         |

|                       | 1               |                   | 7 through F                  | 0111         |

| - œ                   | 202             |                   | 8 through F                  | 1000         |

| σ                     | 24              |                   | 9 through F                  | 1001         |

| , <del>c</del>        | 28              |                   | A through F                  | 1010         |

| 2 =                   | 20              |                   | B through F                  | 1011         |

| : +                   | 90              |                   | C through F                  | 1100         |

| : <u>c</u>            | 34              |                   | D through F                  | 1101         |

| 5 4                   | 38              |                   | E and F                      | 1110         |

| (1 owest priority) 15 | gC              | External device   | F only                       | 1111         |

Fig. 2-22. Interrupt priorities and masking are listed here. (Courtesy of Texas Instruments)

# TMS9900 3 Family Support Chips

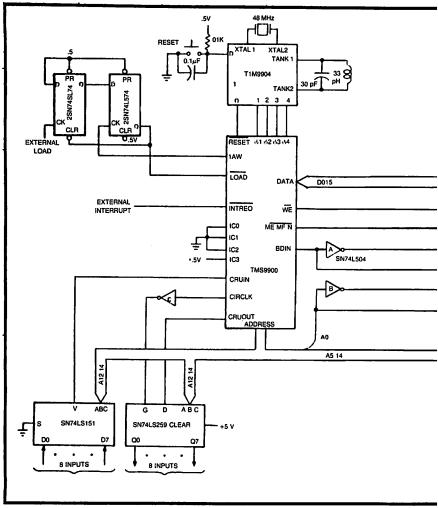

To support the TMS9900 processor, the manufacturer offers a family of devices.

At this writing, the family includes seven chips in addition to the TMS9900, numbered as 9901 through 9907. The first three are prefixed "TMS" (TMS9901 through TMS9903) and the other four bear a "TIM" prefix.

The four TIM devices are also numbered in the 74000 series, and (with the exception of the TIM9904) are referred to in this volume by their 74000-series identities. These are the devices, their 74000-series numbers, and their functions:

- TMS9901 (no other identity) Programmable System Interface—provides up to 15 single-line interrupt coding and up to 16-bit I/O interfacing.

- TMS9902 (no other identity) Asynchronous Communication Controller—interfaces start-stop serial peripherals.

- TMS9903 (no other identity) Synchronous Communication Controller—interfaces serial peripherals which do not use start-stop protocol.

- TIM9904 (74LS362) Clock Generator—provides required four-phase clock signals for entire system.

- TIM9905 (74LS251) 3-State Octal Multiplexer—accepts signal from one of eight addressed input lines and directs it to single output line.

- TIM9906 (74LS259) Octal Addressable Latch—Latches single-line input signal into one of eight addressed output stores.

- TIM9907 (74148) Priority Encoder—produces 3-bit code to indicate highest-priority input signal which is active.

For the purposes of this volume, only the 9901 through 9904 are discussed, since the TMS9901 includes the functions provided by the remaining three chips. The 9901, in fact, is the functional equivalent of two each of the other three chips, although not all this capability can be used at the same time.

#### TMS9901 PROGRAMMABLE SYSTEM INTERFACE

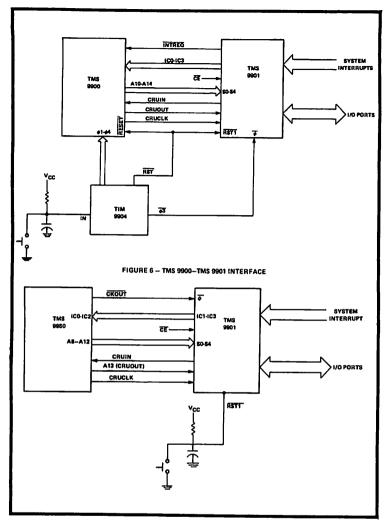

The TMS9901 is a standard 40-pin DIP device (Fig. 3-1) which has 9 CRU-interface lines which communicate with the 9900, 5 interrupt-interface lines which also communicate with the 9900, 22 system-directed lines, a reset pin, two power pins, and a clock input.

The CRU-interface lines are CRUOUT (pin 2), CRUCLK (pin 3), CRUIN (pin 4), Address Select lines S0 through S4, (pins 39, 36, 35, 25, and 24), and Chip Enable (pin 5). The interrupt-interface lines are INTREQ (pin 11) and IC0 through IC3 (pins 15, 14, 13, and 12). The 22 system-directed lines are divided into three buffer

Fig. 3-1. The TMS9901 is supplied in a 40-pin DIP. These are the pin assignments. (Courtesy of Texas Instruments)

Fig. 3-2. Interconnection between TMS9901 and TMS9900 can be as simple as this. Note that 9904 can be replaced by discrete logic. (Courtesy of Texas Instruments)

groups. One primarily serves interrupts, one serves only as I/O, and one can have its bits set individually to be either interrupt or I/O functions.

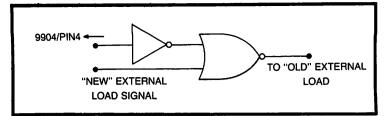

As can be seen from Fig. 3-2, the 9901 directly couples to the 9900; it uses only a decoder circuit to enable the CRU interface (the decoder circuit consists of the circuit shown in Fig. 2-19, to obtain the CRU clocking pulse and a comparator circuit to generate a Chip

Enable when address lines A3 through A9 inclusive contain the correct value). This chip-enable circuit must be active low and will result in making the 9901 relocatable from the zero position, as well as allowing multiple 9901 chips to be used.

The 9901 consists of three buffer groups: buffer group one (normally used for interrupts) consists of six input-output buffers (pins 9, through 17, and 18). They can also be used as input buffers, allowing up to 22 lines to be used as input.

Buffer group two, (pins 23 and 27 through 34) consists of nine bidirectional buffers which can be individually set to behave as either I/O ports or interrupt ports. If a port is predisabled as an interrupt port, then it can be used as an I/O port in safety.

Buffer group three behaves as a series of 1-bit I/O ports (pins 19 through 22, 26, 37, and 38).

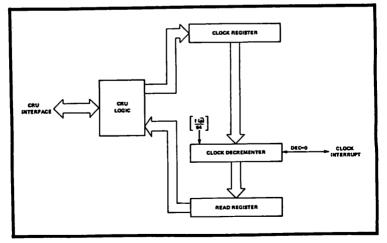

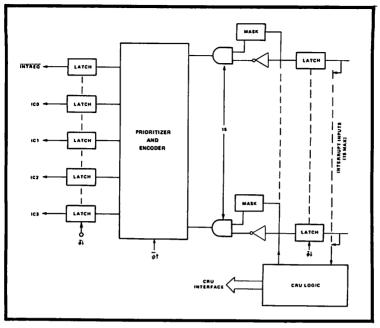

Also included in the 9901 are a real-time clock, which can be controlled and read through the use of CRU commands; a register mask, holding the interrupt masks; a prioritizer and encoder, which converts 15-line code to 4 with latching to generate the interrupt codes; and CRU logic to control the above devices.

The 9901 allows the 9900 to have additional features. One is a true real-time clock, which has an interrupt priority of 3 (see Fig. 3-3). This clock, using the master clock that is usually crystal controlled, can behave either as an interval timer, generating inter-

Fig. 3-3. Here is the real-time clock portion of the 9901 in block diagram form. Clock can be set or read via CRU interface, and produces interrupt when countdown reaches zero. (Courtesy of Texas Instruments)

Fig. 3-4. This circuitry inside the 9901 chip converts up to 15 individual interrupt input lines into the 5-line code required by the 9900. (Courtesy of Texas Instruments)

rupts at controlled intervals, or as an event timer (the count is accessible). The clock can be set with an LDCR instruction, bit 0 on (set to 1). Clock mode can be entered without altering the contents of the clock register, by using the 1-bit instruction SB0, followed by an STCR instruction.

Another feature is a masked interrupt capability, which is somewhat more powerful than the simple priority interrupt of the 9900 itself. As an example, it might be desirable to disable interrupt 10 and allow interrupts 12 and 13 to remain enabled. With the 9900 alone, disabling 10 means disabling 12 and 13 as well. Remember that interrupt priorities sequence the interrupts. If more than one interrupt is active at a time the 9900 will process the highest priority first. Figure 3-4 shows the basic logic of the 9901 interrupt circuits.

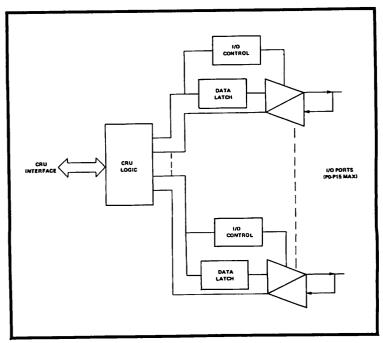

Still another feature provides latched input-output lines for use by the 9900 and external devices. These lines may be altered without fear of an indeterminate state on output. Each line remains in its previous state until specifically changed. Figure 3-5 shows this 9901 feature. The line can be altered (if input) by an external device. The importance of this unit lies in the fact that the CRU logic, including addressing, is already incorporated into the 9901. Note that 7 lines are dedicated to the I/O function and that a maximum of 16 lines may be so used.

### TMS9902 ARCHITECTURE

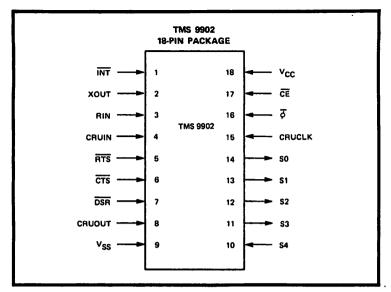

The TMS9902 ACC device (Fig. 3-6) provides the ability to connect to the 9900 an asynchronous device, such as teletypewriters of any kind; ASCII compatible CRTs; keyboard-printer devices such as the TI Silent 700 series or any device using Start-Stop protocol, with a character length of 5 to 8 bits.

The 9902 will further generate any lateral parity option (even, odd, or none) and detect incorrect parity conditions. Even parity means the number of on bits is always kept even by turning an extra bit on and off. Odd parity means the number of bits is always kept odd. No parity means a parity bit is not added.

The transmit and receive rates are independently programmable from approximately 62 bits per second to approximately 76,000

Fig. 3-5. Up to 15 I/O ports configured like this are available to the CRU interface in the 9901 chip. (Courtesy of Texas Instruments)

Fig. 3-6. Basing of the 18-pin TMS9902 package is shown here. Note that only 5 address lines are available. (Courtesy of Texas Instruments)

bits per second. An interval timer is also provided within the 9902, giving a resolution of 64  $\mu$ sec and an interval of up to 16,320  $\mu$ sec.

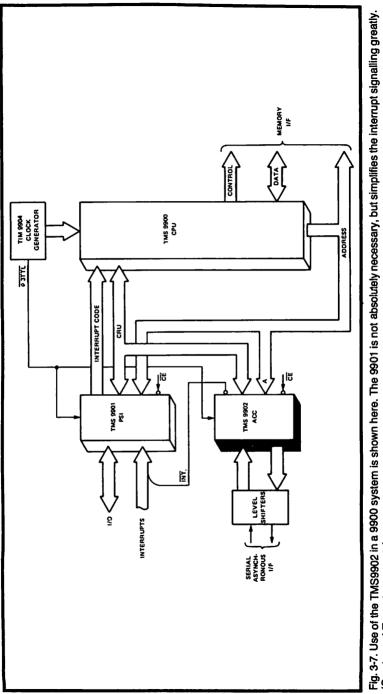

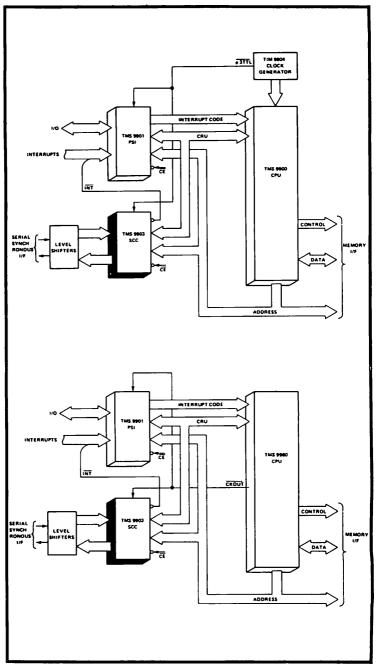

If used within a combination system (see Fig. 3-7) containing a 9901, the 9902 provides an extra interval timer. This extra timer could be used for purposes other than that of the one in the 9901.

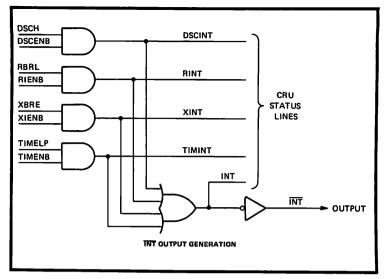

The 9902 provides four different interrupts, which are output as one interrupt level (Fig. 3-8). The actual cause of the interrupt can be deciphered through the CRU interface.

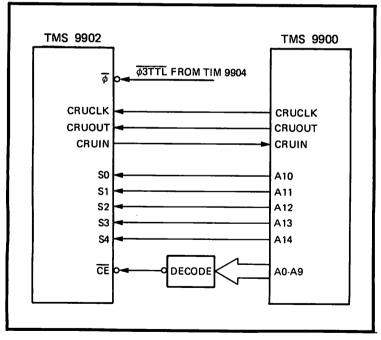

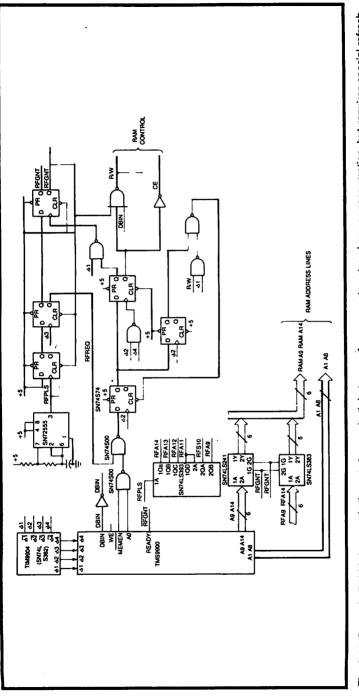

Figure 3-9 shows how the 9900 and the 9902 (or the 9980 and the 9902) are connected together. The decode logic consists of that shown in Fig. 2-19 combined with a hardwired (or plug-alterable) comparator for address lines A3 through A9.

The two chips communicate over the CRU, using 32 bits as command words (see Figs. 3-10, 3-11, and 3-12). There are six registers in the 9902 which are available to the 9900. One is the control register, which is used to set the stop bit length (one, one and a half or two); the parity (none, even or odd); the master clock rate (divide the input clock by either 3 or 4); and the character length (5, 6, 7 or 8 bits). The others are the interval timer, and the receive data rate, transmit data rate, transmit buffer, and receive buffer registers.

Fig. 3-7. Use of the TMS9902 in a 9900 system is shown here. The 9901 is not absolutely necessary, but simplifies the interrupt signalling greatly. (Courtesy of Texas Instruments)

Fig. 3-8. Relationship between the 9902 status conditions and its generation of an interrupt request is shown by this logic. (Courtesy of Texas Instruments)

Fig. 3-9. Direct connections between a 9902 and the 9900 can be made as shown in this diagram. Note that the chip enable decode is not shown; see text for details. (Courtesy of Texas Instruments)

|                                        |               |           | Enable.                                  |                        |                              |                           |          |                    |             |                       |                        |                                  | it                               | tate, Transmit Data Rate,                                 |                               |

|----------------------------------------|---------------|-----------|------------------------------------------|------------------------|------------------------------|---------------------------|----------|--------------------|-------------|-----------------------|------------------------|----------------------------------|----------------------------------|-----------------------------------------------------------|-------------------------------|

| DESCRIPTION                            | Reset device. | Not used. | Data Set Status Change Interrupt Enable. | Timer Interrupt Enable | Transmitter Interrupt Enable | Receiver Interrupt Enable | Break On | Request to Send On | Test Mode   | Load Control Register | Load Interval Register | Load Receiver Data Rate Register | Load Transmit Data Rate Register | Control, Interval, Receive Data Rate, Transmit Data Rate, | and Transmit Buffer Registers |

| NAME                                   | RESET         |           | DSCENB                                   | TIMENB                 | XBIENB                       | RIENB                     | BRKON    | RTSON              | TSTMD       | LDCTRL                | LDIR                   | LRDR                             | LXDR                             | -                                                         |                               |

| ADDRESS10                              | 31            | 30-22     | 21                                       | 20                     | 19                           | 18                        | 17       | 16                 | 15          | 14                    | 13                     | 12                               | 1                                | 10-0                                                      |                               |

| ADDRESS <sub>2</sub><br>S0 S1 S2 S3 S4 | 1 1 1 1       |           | 10101                                    | 10100                  | 1 0 0 1 1                    | 10010                     | 10001    | 10000              | 0 1 1 1 1 1 | 0 1 1 1 0             | 0 1 1 0 1              | 0 1 1 0 0                        | 0 1 0 1 1                        |                                                           |                               |

\_\_\_\_

Fig. 3-10. Output bit address assignments for the 9902 are shown in this listing. Internal conditions for the chip are established by writing data to these bit addresses. (Courtesy of Texas Instruments)

| <br>_ |        | -    |       |      |          |           |                                       |

|-------|--------|------|-------|------|----------|-----------|---------------------------------------|

| 31    | 30     | 29   | 28    | 27   | 26       | 25        | 24                                    |

| RESET |        |      |       |      | NOT USED |           |                                       |

|       |        |      |       |      |          |           |                                       |

| 15    | 14     | 13   | 12    | 11   | 10       | 9         | 8                                     |

| TSTMD | LDCTRL | LDIR | LRDR  | LXDR | CONTR    | IOL, INTE | RVAL, RECEIVE                         |

| 1     | 1      |      | 1 1   |      |          | r         | 1                                     |

| l     | 1      |      | 1 1   |      |          |           | 1                                     |

| 1     | 11     | x    | 1 × 1 | x    | 1        | 1         | 1                                     |

| I     |        | ~    | 1 ^ 1 | ~    | 1        |           | 1                                     |

| 1     |        |      | 1 1   |      | 1 1      | 1         | 1                                     |

|       | •      |      | •     |      |          |           | •                                     |

|       |        |      | 1 1   | 1    |          |           | 1                                     |

|       |        |      | •     |      |          |           |                                       |

|       |        |      |       |      |          |           |                                       |

| ļ     | .      |      | i     |      | 1        |           | 1                                     |

|       |        |      |       |      |          |           |                                       |

| l     | o      | 1    | ×     | x    |          |           | 1                                     |

| ĺ     | . I    |      | 1 1   |      |          | I         | 1                                     |

|       |        |      | 1 1   |      | l l      |           | I                                     |

| 1     | L 1    |      | F I   |      |          | l         | i .                                   |

|       | 1      |      | 1 1   | 1    | 1        |           | 1                                     |

| I     | 0      | 0    | 1 1   | x    | RDV8     | RDR9      | RDR8                                  |

|       | •      |      |       | , i  |          |           | · · · · · · · · · · · · · · · · · · · |

| 1     |        |      | 1 1   | l    |          |           |                                       |

|       |        |      |       |      |          |           |                                       |

|       |        |      |       |      |          |           | 1                                     |

|       |        |      | 1 4   |      |          |           | <u></u>                               |

| 1     | 0      | 0    | ×     | 1    | XDVB     | XDR9      | XDR8                                  |

|       | •      |      | i i   |      |          |           | 1                                     |

| 1     | I      |      | 1 1   | 4    |          |           | 1                                     |

| 1     | I      |      | 1 1   | 1    |          |           | 1                                     |

| •     | •      |      | • •   |      |          |           | 1                                     |

| 1     | 0      | 0    | 0     | 0    | i I      |           | 1                                     |

|       | •      |      | •     |      | •        |           | •                                     |

|       |        |      |       |      |          |           |                                       |

|       |        |      |       |      |          |           |                                       |

|       |        |      |       |      |          |           |                                       |

Fig. 3-11. This chart shows in greater detail how the 9902 is set up by writing to specific output bit addresses. The STCR command is used to set bits into addresses 0 through 10, after appropriate values are written into addresses 14 through 11. (Courtesy of Texas Instruments)

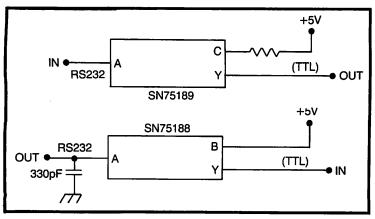

Further data available to the 9900 (and the programmer) includes status flags and error flags. The 9902 interfaces to the outside world through TTL compatible circuits. There are times when an

|     | 23      | 22       | 21                    | 20             | 19                | 18            | 17        | 16       |

|-----|---------|----------|-----------------------|----------------|-------------------|---------------|-----------|----------|

|     |         |          | DSCENB                | TIMENB         | XBIENB            | RIENB         | BRKON     | RTSON    |

|     |         |          |                       |                |                   |               |           |          |

|     | 7       | 6        | 5                     | 4              | 3                 | 2             | 1         | 0        |

|     | DATA    | RATE, TR | ANSMIT DA             | TA RATE,       | AND TRANS         | SMIT BUFF     | ER REGIST | ERS      |

|     |         |          |                       |                |                   |               |           |          |

| 1   | l       |          |                       |                | l                 |               |           |          |

| _   |         |          |                       |                | REGISTER          |               |           |          |

|     | SBS1    | SBS2     | PENB                  | PODD           | CLK4M             | -             | RCL1      | RCLO     |

| ,   |         |          | ·                     |                | 1                 |               |           | <i>`</i> |

| 1   | Stop    | Bits     | Pa                    | rty            | fint =            |               | Character | Length   |

|     | 00      | 1-1/2    | . ox                  | none           |                   |               | 00        | 5        |

| I   | 01      | 2        | 10                    | even           | f∲/(3+CL)         | <b>(4M)</b> . | 01        | 6        |

|     | 1X      | 1        | 11                    | odd            |                   |               | 10        | 7        |

|     |         | 1        |                       |                |                   |               | 11        | 8        |

| I   |         |          |                       | l<br>          |                   |               |           |          |

| r   | 7107    | TMR 6    | TMR5                  | TMR4           | REGISTER          | TMR2          | TMR1      | TMRO     |

| L   | TMR7    | T MIN O  | TWIND                 |                | 10015             |               |           |          |

| L L |         |          | 1                     | 1              | ·                 |               |           |          |

| I   | !       |          | 1                     |                | MR<br>t X 64 X TM | 8             |           |          |

| 1   |         | 1        | I I                   | ')   VL<br>    | 1                 |               |           |          |

| 1   |         | 1        | RECI                  | I<br>EIVE DATA | RATE REG          | ISTER         |           |          |

|     | RDR7    | RDR6     | RDR5                  | RDR4           | RDR3              | RDR2          | RDR1      | RDRO     |

|     |         |          | L                     |                |                   |               |           |          |

| ī   |         |          |                       | DR             | 1                 |               |           |          |

|     |         | frev     | / = fint ÷.8 f        |                | R ÷ 2             |               |           |          |

| 1   |         | 1        | 1                     | 1              | 1                 |               |           |          |

| •   |         | TRA      | SMIT DAT              | A RATE RE      | GISTER            |               |           |          |

|     | XDR7    | XDR6     | XDR5                  | XDR4           | XDR3              | XDR2          | XDR1      | XDR0     |

|     |         |          |                       |                |                   |               |           |          |

|     |         |          | l x                   | Y<br>DR        | 1                 |               |           |          |

|     |         | fxm      | t = fint $\div 8^{X}$ | DV8 ÷ XD       | R ÷ 2             |               |           |          |

|     |         | 1        | 1                     | I              | ł                 |               |           |          |

| _   |         | TRA      | ANSMIT BU             | FFER REG       | ISTER             |               |           |          |

| [   | XBR7    | XBR6     | XBR5                  | XBR4           | X8R3              | XBR2          | XBR1      | XBRO     |

|     |         |          |                       |                |                   |               |           |          |

|     | NOTE 1: |          | OF THE BI             |                |                   | _             | THE LOAD  | CONTROL  |

|     |         | FLAG FOF | THAT RE               | SISTER TO      | BE AUTOM          | ATICALLY      | HESE I.   |          |

|     |         |          |                       |                |                   |               |           |          |

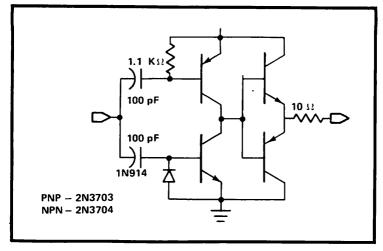

RS232 compatible interface is desired. This can be accomplished by the two circuits in Fig. 3-13.

# TMS9903 SYNCHRONOUS COMMUNICATION CONTROLLER

Very little will be said about this integrated circuit, since it is rather doubtful that the typical user would be interested in actually

|            | AD | DRE | SSg |    |           |           | <u> </u>                                         |

|------------|----|-----|-----|----|-----------|-----------|--------------------------------------------------|

| <b>S</b> 0 | 51 | 82  | \$3 | 84 | ADDRESS10 | NAME      | DESCRIPTION                                      |

| 1          | 1  | 1   | 1   | 1  | 31        | INT       | Interrupt                                        |

| 1          | 1  | 1   | 1   | 0  | 30        | FLAG      | Register Load Control Flag Set                   |

| 1          | 1  | 1   | 0   | 1  | 29        | DSCH      | Data Set Status Change                           |

| 1          | 1  | 1   | 0   | 0  | 28        | CTS       | Clear to Send                                    |

| 1          | 1  | 0   | 1   | 1  | 27        | DSR       | Data Set Ready                                   |

| 11         | 1  | 0   | 1   | 0  | 26        | RTS       | Request to Send                                  |

| 1          | 1  | 0   | 0   | 1  | 25        | TIMELP    | Timer Elapsed                                    |

| 1          | 1  | 0   | 0   | 0  | 24        | TIMERR    | Timer Error                                      |

| 1          | 0  | 1   | 1   | 1  | 23        | XSRE      | Transmit Shift Register Empty                    |

| 1          | 0  | 1   | 1   | 0  | 22        | XBRE      | Transmit Buffer Register Empty                   |

| 1          | 0  | 1   | 0   | 1  | 21        | RBRL      | Receive Buffer Register Loaded                   |

| 1          | 0  | 1   | 0   | 0  | 20        | DSCINT    | Data Set Status Charge Interrupt (DSCH * DSCENB) |

| 1          | 0  | 0   | 1   | 1  | 19        | TIMINT    | Timer Interrupt (TIMELP • TIMENB)                |

| 1          | 0  | 0   | 1   | 0  | 18        |           | Not used (always = 0)                            |

| 1          | 0  | 0   | 0   | 1  | 17        | XBINT     | Transmitter Interrupt (XBRE • XBIENB)            |

| 1          | 0  | 0   | 0   | 0  | 16        | RBINT     | Receiver Interrupt (RBRL • RIENB)                |

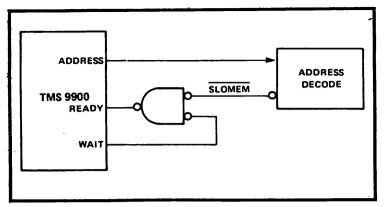

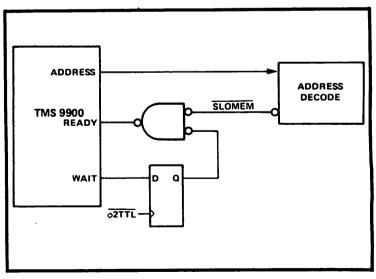

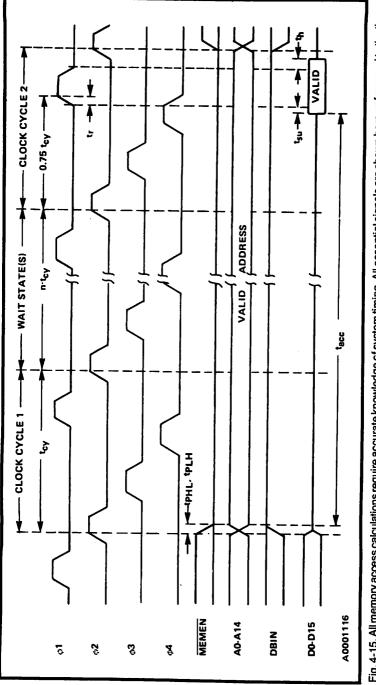

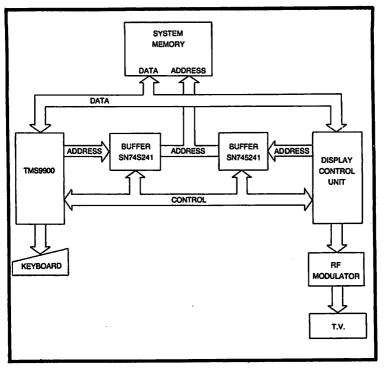

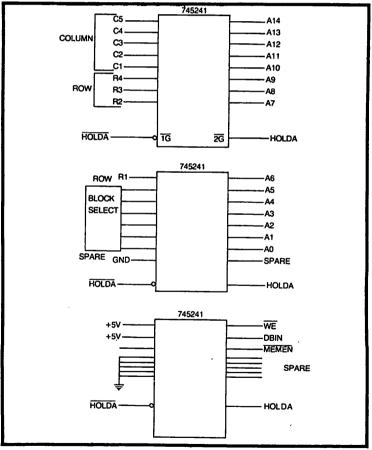

| 0          | 1  | 1   | 1   | 1  | 15        | RIN       | Receive Input                                    |